## PATENT ABSTRACTS OF JAPAN

(11)Publication number:

07-083980

(43) Date of publication of application: 31.03.1995

(51)Int.Cl.

G01R 29/02 G01R 23/16

(21) Application number: **05-233365**

(71)Applicant: ADVANTEST CORP

(22) Date of filing:

20.09.1993

(72)Inventor: UJIIE HITOSHI

## (54) JITTER/WANDER ANALYZER

## (57) Abstract:

PURPOSE: To provide a jitter/wander analyzer which can accurately, efficiently measure and analyze a jitter, a wander reduced in its frequency.

CONSTITUTION: A measuring unit 10 has a measurement signal generator 11, a reference oscillator 12, a frequency converter 13, a multiplier 14, a jitter adding circuit 15, a switching circuit 16, first and second continuous period measuring circuits 17, 18, first and second buffer memories 19, 20, and first and second frequency dividers 21, 22. The circuits 17, 18 continuously measure a period of a signal to be measured. The variations in data of signal periods undergo fast Fourier transform in an arithmetic analyzer 30 to analyze a jitter and analyzes a relative jitter from time interval measured value of the two signals to be measured. On the other hand, frequencies of the signals to be measured are suitably divided by the dividers 21, 22 to analyze its low frequency jitter, and a wander is analyzed by simultaneously calculating MTIE (maximum time interval error) and long frequency deviations at a plurality of observation times.

## (19)日本国特許庁 (JP)

# (12) 公開特許公報(A)

## (11)特許出顧公開番号

# 特開平7-83980

(43)公開日 平成7年(1995)3月31日

(51) Int.Cl.<sup>6</sup>

識別配号

FΙ

技術表示箇所

G01R 29/02

L

سظ

23/16

A 8803-2G

庁内整理番号

審査請求 未請求 請求項の数8 OL (全 21 頁)

(21)出願番号

特職平5-233365

(71)出願人 390005175

株式会社アドバンテスト

東京都練馬区旭町1丁目32番1号

(22)出顯日

平成5年(1993)9月20日

(72)発明者 氏家 仁

宮城県仙台市青葉区上愛子字松原48番2

株式会社アドバンテスト仙台研究所内

(74)代理人 弁理士 草野 卓 (外1名)

## (54) 【発明の名称】 ジッタ/ワンダ解析装置

#### (57) 【要約】

【目的】 低周波数化したジッタやワンダを高精度に、 効率よく測定及び解析することができるジッタ/ワンダ 解析装置を提供する。

【構成】 測定信号生成回路11と、基準発振器12と、周波数変換回路13と、逓倍回路14と、ジッタ付加回路15と、切り替え回路16と、第1及び第2のが連続周期測定回路17及び18と、第1及び第2のが周器21、22とから測定部10を構成する。連続周期測定回路17、18で被測定信号の周期を連続的に測定し、演算解析部でそれらの周期データの変動を高速フーリエ変換してジッタを解析し、また、2つの被測定信号の時間隔隔の周波数を分周器21、22により適当に分周して低周波ジッタを解析し、また、ワンダは複数の観測時間におけるMTIEや長期周波数偏差を同時に算出して解析する。

#### 【特許請求の範囲】

【請求項1】 パルス状の被測定信号の一方のエッジが 与えられ、該エッジの周期を連続的に測定する第1の連 続周期測定回路と、

パルス状の被測定信号の一方のエッジ又は装置内部で作られた基準位相の所定の周波数の試験信号の一方のエッジが与えられ、該エッジの周期を連続的に測定する第2の連続周期測定回路と、

前記第1及び第2の連続周期測定回路から出力される測 定周期データを記憶するための第1及び第2のメモリ と。

前記第1及び第2のメモリに記憶された測定周期データ に基づいて、前記被測定信号の少なくとも周期、時間間 隔を含む時間/周波数の諸量を算出する測定量演算手段 と、

算出された被測定信号の時間/周波数の諸量の解析を行う解析手段と、

前記第1及び第2の連続周期測定回路に入力される被測 定信号をそれぞれ選択的に分周する第1及び第2の分周 手段とを具備することを特徴とするジッタ/ワンダ解析 装置。

【請求項2】 前記被測定信号の時間/周波数の諸量の解析を行う解析手段は、前記測定量演算手段で算出された測定値の経過時間に対する変化量を高速フーリエ変換して解析した結果から被測定信号のジッタ周波数スペクトラムを求める手段を含むことを特徴とする請求項1に記載のジッタ/ワンダ解析装置。

【請求項3】 前記第1及び第2の連続周期測定回路で2つの被測定信号の周期を同時に、かつ連続的に測定し、前記解析手段により、前記測定量演算手段で算出された各々の測定値の経過時間に対する変化量を高速フーリエ変換して解析した結果から各々の被測定信号のジッタ圏波数スペクトラムを同時に求めることを特徴とする請求項1に記載のジッタノワンダ解析装置。

【請求項4】 前記第1及び第2の連続周期測定回路で2つの被測定信号の周期を同時に、かつ連続的に測定し、前記測定量演算手段で各々の周期測定値より両信号間の時間間隔値を算出し、前記解析手段により、前記測定量演算手段で算出された時間間隔値の経過時間に対する変化量を高速フーリエ変換して解析した結果から相対的なジッタ周波数スペクトラムを求めることを特徴とする請求項1に記載のジッタ/ワンダ解析装置。

【請求項5】 前記第1及び第2の分周手段により被測定信号を適当な周波数まで分周し、その分周周期を前記第1及び第2の連続周期測定回路で測定することによって全体の測定時間を長くし、前記解析手段により、前記測定量演算手段で算出された測定値の経過時間に対する変化量を高速フーリエ変換して解析した結果から被測定信号の比較的低いジッタ周波数スペクトラムを求めることを特徴とする請求項1に記載のジッタ/ワンダ解析装

置。

【請求項7】 前記基準位相の所定の周波数の試験信号にジッタを付加して、このジッタ付加試験信号を外部へ出力するジッタ付加手段をさらに含み、該ジッタ付加手段からユーザが設定できる任意の波形や周波数のジッタ付加試験信号を外部の被試験装置に出力して該被試験装置からの出力信号を被測定信号として入力することにより、該被試験装置のジッタ抑圧効果やジッタ耐力を解析できるようにしたことを特徴とする請求項1に記載のジッタ/ワンダ解析装置。

【請求項8】 前記基準位相の所定の周波数の試験信号を外部へ出力するための端子を含み、該端子よりこのジッタのない純粋な試験信号を外部の被試験装置に出力して該被試験装置からの出力信号を被測定信号として入力することにより、該被試験装置のみで発生するジッタを解析できるようにしたことを特徴とする請求項1に記載のジッタ/ワンダ解析装置。

### 【発明の詳細な説明】

[0001]

【産業上の利用分野】この発明は、一般的には、パルス状の被測定信号のパルス幅の変動(ゆれ)、いわゆるジッタを解析するジッタ解析装置と、MTIE(MAXIMUM I IME INTERVALERROR)による長期的位相変動であるワンダを解析するワンダ解析装置との両機能を備えたジッタ/ワンダ解析装置に関し、特に、パルス状の被測定信号における時間/周波数領域の諸量、例えば周期、時間間隔などを連続的に測定し、その測定量からジッタの振幅と周波数成分、及びMTIEによるワンダを高精度に、効率よく解析することができるジッタ/ワンダ解析装置に関するものである。

#### [0002]

【従来の技術】ISDNやSONET/SDH等のアーキテクチャで代表されるディジタル通信ネットワークでは、高品質で大容量の高速伝送実現を妨げる主たる要因として、ジッタやワンダが考えられる。ジッタは、ITU/TS(旧CCITT)の勧告などで、その振幅量と周波数成分が規定され、同じくワンダは観測時間に対す

るMTIEの最大値が規定されている。

【0003】一般に、伝送通信システムでは受信クロックの再生に比較的ゲインの低いPLL(フェーズロックループ)が用いられている。このため、高周波成分のジッタはPLLによってある程度抑圧されるが、PLLで除去しきれない低周波成分のジッタやワンダが実際の運用上問題になる。さらに、今後の社会基盤として重要なSONET/SDHでは、ネットワーク・インタースにおける同期維持のために、伝送フレームの先子のこれがよりでは、タイムスタンプによって頭が、また、ATM(非同期転送モード)では、タイムスタンプによって頭が、また、ATM(非同期転送モード)では、タイムスタンプによって動き続元の基準周波数情報を接続先へ伝達し、接続元の基準周波数を接続先で再現する機能を有するが、これらの新しい同期技術はまた、新しい更なる低周波ジッタ( $1\mu$ 日本~10日本)並びにワンダという問題を生み、ジッタの低周波化が懸念されている。

#### [0004]

《発明が解決しようとする課題》 従来よりディジタル・ トランスミッション・アナライザはパルス状の被測定信 号のジッタを解析できるものとして知られている。この ディジタル・トランスミッション・アナライザは伝送エ ラーやジッタを測定する試験装置であり、主に送信部と 受信部とで構成されている。受信部にジッタの測定機能 があるが、測定できるのはジッタ振幅や、あるジッタ振 幅値を越えたときの発生頻度の測定が主であり、周波数 成分解析機能はないと言える。何故ならば、このディジ タル・トランスミッション・アナライザでジッタの周波 数成分解析を行う場合には、送信部で出力信号のジッタ 周波数を設定し、受信部でそのときのジッタ振幅を測定 するというやり方以外に方法がなく、従って、低周波か ら高周波までの連続的なジッタ周波数成分解析を行うこ とはできないからである。また、ジッタ周波数の設定領 域も下限が10Hz~100Hz程度で低周波ジッタ解 析には不十分であり、ワンダに関しては測定できない。 〖0005〗また、従来公知のSONET/SDHアナ ライザは、一般的に、ファンクション試験が主である が、一部の機種にジッタ/ワンダ解析が可能なものがあ る。この機種のものは、上記ディジタル・トランスミッ ション・アナライザと同様に、送信部と受信部に分かれ て構成され、送信部でジッタ周波数と振幅を設定し、受 信部でジッタ振幅を測定するものであるが、ジッタ周波 数設定領域の下限が1Hzと低く、従って、ジッタ解析 も1Hzまでは可能であるが、1Hzではまだ不十分で ある。また、100m秒(0. 1秒)から100秒まで の観測期間におけるワンダ測定(MTIE)機能もあ る。しかしながら、この観測期間はITU/TSの観測 期間勧告の範囲の極く一部に過ぎず、極めて不十分であ

【0006】現在、ITU/TS勧告で明らかにされているMTIEの観測期間は50m秒~10<sup>9</sup> 秒の範囲で

あるが、50m 秒~500 秒の範囲と500 秒~109 秒の範囲の2 段階に分けてある。その内50m 秒から107 秒までの範囲が観測期間の現実性からワンダとして重要視される(G. 811 勧告)。よって、上記0.1 秒から100 秒までの観測期間ではワンダを高精度に測定することは不可能である。

【0007】この発明の目的は、低周波数化したジッタを高精度に測定及び解析することができ、かつワンダについてもITU/TS勧告のMTIEによるワンダを高精度に、効率よく測定及び解析することができるジッタ/ワンダ解析装置を提供することにある。

## [0008]

【課題を解決するための手段】この発明では、パルス状 の被測定信号の一方のエッジが与えられ、該エッジの周 期を連続的に測定する第1の連続周期測定回路と、パル ス状の被測定信号の一方のエッジ又は装置内部で作られ た基準位相の所定の周波数の試験信号の一方のエッジが 与えられ、該エッジの周期を連続的に測定する第2の連 続周期測定回路と、前記第1及び第2の連続周期測定回 路から出力される測定周期データを記憶するための第1 及び第2のメモリと、前記第1及び第2のメモリに記憶 された測定周期データに基づいて、前記被測定信号の少 なくとも周期、時間間隔を含む時間/周波数の諸量を算 出する測定量演算手段と、算出された被測定信号の時間 /周波数の諸量の解析を行う解析手段と、前記第1及び 第2の連続周期測定回路に入力される被測定信号をそれ ぞれ選択的に分周する第1及び第2の分周手段とを設 け、前記第1及び第2の連続周期測定回路で2つの被測 定信号の周期を同時に、かつ連続的に測定することを可 能にし、前記解析手段により、前記測定量演算手段で算 出された各々の測定値の経過時間に対する変化量を高速 フーリエ変換して解析した結果から各々の被測定信号の ジッタ周波数スペクトラムを同時に求めることができる ようにしたものである。

【0009】また、前記測定量演算手段で各々の周期測定値より両信号間の時間間隔値を算出し、前記解析手段により、前記測定量演算手段で算出された時間間隔値の経過時間に対する変化量を高速フーリエ変換して解析した結果から相対的なジッタ周波数スペクトラムを求めることができるようにしたものである。また、前記第1及び第2の分周周期を前記第1及び第2の連続周期で回路で測定することによって全体の測定時間を長い、前記解析手段により、前記測定量演手段で算出をし、前記解析手段により、前記測定量演手段で算出を換して解析した結果から被測定信号の比較的低いジッタ周波数スペクトラムを求めることができるようにしたものである。

【0010】また、前記第1及び第2の分周手段により 被測定信号と前記基準位相の所定の周波数の試験信号と をそれらの周波数が一致する適当な周波数までそれぞれ分周し、各々の分周信号の周期を前記第1及び第2の連続周期測定回路でそれぞれ測定し、前記測定量演算手段で各々の分周周期測定値より両信号間の時間間隔値を算出し、前記解析手段により、前記測定量演算手段で算出された前記両信号間の時間間隔値よりその最大値と最小値をそれぞれ算出するとともに、それらから複数の観測時間におけるMTIEや長期周波数偏差を同時に算出し、長期的位相変動であるワンダを効率よく解析できるようにしたものである。

【 O O 1 1 】また、前記基準位相の所定の周波数の試験 信号にジッタを付加して、このジッタ付加試験信号を外 部へ出力するジッタ付加手段を設け、該ジッタ付加手段 からユーザが設定できる任意の波形や周波数のジッタ付 加試験信号を外部の被試験装置に出力して該被試験装置 からの出力信号を被測定信号として入力することによ り、該被試験装置のジッタ抑圧効果やジッタ耐力を解析 できるようにしたものである。

【〇〇12】さらに、前記基準位相の所定の周波数の試験信号を外部へ出力するための端子を設け、該端子よりこのジッタのない純粋な試験信号を外部の被試験装置に出力して該被試験装置からの出力信号を被測定信号として入力することにより、該被試験装置のみで発生するジッタを解析できるようにしたものである。

#### [0013]

【作用】上記この発明の構成によれば、前記解析手段により、前記測定量演算手段で算出された測定値の経過時間に対する変化量を高速フーリエ変換して解析した結果から被測定信号のジッタ周波数スペクトラムを求めることができるから、低周波から高周波までの連続的なジッタ周波数成分解析を高精度に行うことができる。また、分周手段で被測定信号を適当な周波数まで分周することにより、低周波ジッタの解析も十分に行え、さらに、ワンダに関してもITU/TSで勧告しているMTIEによるワンダを重要視されている50m秒から10~秒までの観測期間にわたって高精度に、効率よく測定することができる。

## [0014]

《実施例》以下、この発明の実施例について図面を参照

| 分周比 | 測定値取得間隔       | 全測定時間  |

|-----|---------------|--------|

| 1   | 488ns         | 488ms  |

| 2   | 977ns         | 977ms  |

| 4   | 1. 95μs       | 1. 95s |

| 8   | 3. $91 \mu s$ | 3. 91s |

| 16  | 7. 81 $\mu$ s | 7.81s  |

| 3 2 | 15.63 µs      | 15.63s |

となり、長周期ジッタの解析が可能になる。

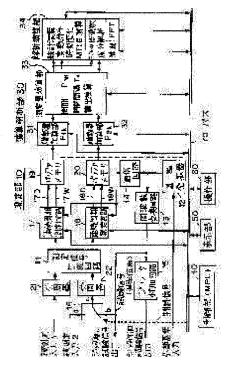

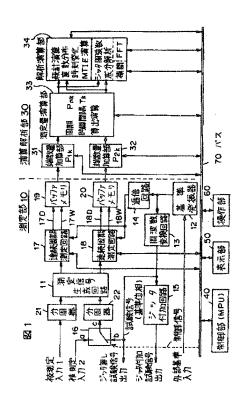

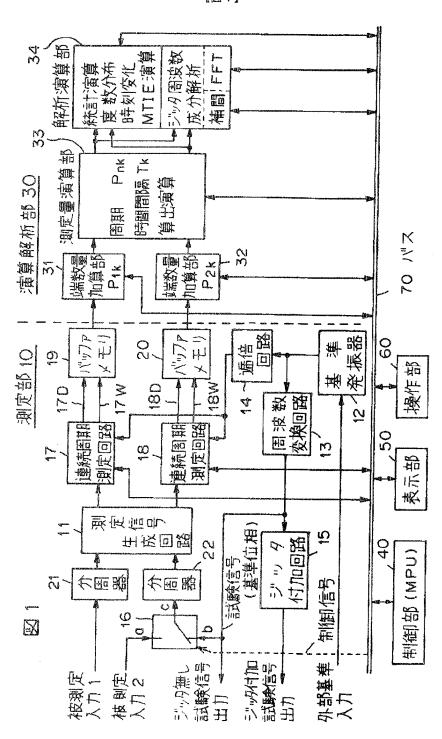

【OO17】また、本解析装置はITU/TSで勧告しているMTIEによるワンダを解析することができる。 この場合、同勧告書内のワンダ測定例と同じく、被測定 して詳細に説明する。図1はこの発明によるジッタ/ワンダ解析装置の一実施例の全体構成を示すブロック図である。本実施例のジッタ/ワンダ解析装置は、パルス状の被測定信号における時間/周波数領域の諸量、例えば、側期、時間間隔などを連続的に高精度に測定することができるとともに、データ取得時の時刻を明らかにして、これら諸量の統計演算、度数分布、経過時間に対すると、、大田できるものであり、測定部10と、演算解析部30と、制御部40と、表示部50と、操作部60はバス70を介して測定部10及び演算解析部30と相互に接続されている。

【0015】測定部10は測定信号生成回路11と、基 準発振器12と、周波数変換回路13と、逓倍回路14 と、ジッタ付加回路15と、切り替え回路16と、第1 及び第2の連続周期測定回路17及び18と、第1及び 第2のバッファメモリ19及び20と、第1及び第2の 分周器21、22とから構成されている。本実施例のジ ッタ/ワンダ解析装置は連続周期測定回路の周期測定値 を用いてジッタの解析を行う。本解析装置には2つの連 続周期測定回路17、18が設けられているから、2つ の被測定信号を入力して各々の信号に対してのジッタ解 析が行える。被測定信号は、連続周期測定回路が可能な 限り、周期を空き時間無しで連続的に測定する。また、 2つの被測定信号を入力して、その時間間隔測定値か ら、一方の入力に対する相対的なジッタを解析すること もできる。この場合、時間間隔測定値は、2つの連続周 期測定回路17、18の周期測定値の積算である経過時 間から両者の時間間隔を導出し、その値の解析を行う。 【0016】一方、低周波ジッタの解析には長い測定時 間が必要であることから、本解析装置では被測定信号の 周波数を内部で分周器21、22により適当に分周し、 個々の測定値取得間隔を長くして全体の測定時間を長く することで、低周波ジッタを解析する。例えば、被測定 信号が2048KHz、バッファメモリ19、20の容 量が1Mワードであるならば、その分周比と測定時間 は、

信号と内部のジッタ付加前の試験信号を共に分周器2 1、22で4KHzに分周し、両者の連続周期が測定される。その周期測定値はいったんバッファメモリ19、20に記憶されるが、演算解析部30は、可能な限り逐 次、周期測定値をバッファメモリ19、20から呼び出し、計数クロックによる計数値と端数時間測定値を加算して時間間隔値を算出し、ユーザが設定する観測時間内での時間間隔測定値の最大値と最小値を求めて、メモリ(データ数が比較的少ないので、CPUのシステムメモリを使用)に記憶しておき、全ての測定値取得が終了した後、各観測時間に対するMTIEを算出し、データとグラフ表示する。

【0018】このとき、測定値取得間隔時間は250μ s であることから、1Mワードのバッファメモリ容量で は観測時間の最大が250sまでしか設定できないの で、この問題を解決するために、バッファメモリへの書 き込みは、最終アドレスにデータを書き込んだ後は、先 頭アドレスに戻るように、アドレスカウンタを巡回させ る。測定値取得間隔時間が250 µ sと比較的遅いた め、CPUは測定値を溜めることなく逐次データを読み 込むことができるので、アドレスの巡回が可能である。 【0019】さらに、本解析装置では、装置内部でジッ タを含んだ試験信号を発生することができ、このジッタ を付加した試験信号を被試験装置である、例えばネット ワーク・クロック供給装置などへ従属基準信号として入 力し、その従属同期出力を本解析装置への被測定信号と して入力して、ジッタやMTIEを解析して、被試験装 置の不要ジッタ出力のチェック、ジッタ抑圧効果、ジッ タ耐力性能等を確認することができる。

【0020】測定信号生成回路11は第1及び第2の分 周器21及び22を介してそれぞれ送られてくる2つの 入力(入力1、入力2)を独立に受信できるように構成 されており、パルス信号のようなパルス状の第1の被測 定信号生成回路11に入力1として供給され、また、 ルス信号のようなパルス状の第2の被測定信号生成回路11に入力1として供給され、 ルス信号のようなパルス状の第2の被測定信号のようなパルス状の第3からのジッタ付加の 基準位相の試験信号が切り替え回路16で選択されて別 定信号生成回路11に入力2として供給される。この測 定信号生成回路11に入力2として供給される。この測 定信号生成回路11は2系統の被測定信号のエッジ入力 シーケンスを決定する。なお、後述するように、測定信 号生成回路11は周期に関しては2系統の別個の被測定 信号の同時測定が可能なように構成されている。

【0021】切り替え回路16は被測定信号を2系統入力して各々のジッタを解析したり、相対的なジッタを解析したい場合、その可動接点cが第1の固定接点aに接続され、被測定入力2を第2の分周器22を介して測定信号生成回路11へ入力2として供給する。これに対し、ワンダ測定時には可動接点cが第2の固定接点bに接続され、基準発振器12から周波数変換回路13を介して供給される基準位相の試験信号が第2の分周器22を介して測定信号生成回路11へ入力2として供給される。切り替え回路16は制御部40からの指令(制御信号)に従って、外部の被測定信号(被測定入力2)或い

は内部の基準位相の試験信号のいずれかを選択して、第 2の分周器 2 2に送る。切り替え回路 1 6 はリレー等の機械的スイッチであっても、ゲートによる論理的スイッチであってもよい。

【0022】第1の分周器21は比較的高い周波数のジッタを解析する場合には、被測定入力1を分周せずにそのまま測定信号生成回路11へ入力する。一方、低周波数ジッタやワンダを解析する場合には、被測定入力する。第2の分周して測定信号生成回路16を通じて供給されるジッタを付加する前の基準位相の試験信号を4KHzに分周の分を行って、切り替え回路16が被測定入力2を必要には、この被測定入力2を必要には、この被測定入力2を必要には、この被測定入力2を必要ににな分周して測定信号生成回路11へ入力する。上には、この被測定入力2を必要にじて分周して測定信号生成回路11へ入力する。上に分周とび第2の分周器21、22は測定条件に応第1及び第2の分周器21、22は測定条件に応第1とが切り替えられるように、プログラマブル分周器で構成する。

【0023】基準発振器12は本解析装置のタイムベー スであり、周波数が極めて安定な発振器、例えば恒温槽 入りの水晶発振器などを使用する。基準発振器12には 必要に応じて外部基準信号、例えばUTC(協定世界 時)に同期した外部基準周波数信号を供給し、発振周波 数を同期させる。基準発振器12の出力信号は周波数変 換回路13に供給され、その周波数が試験信号の周波数 に変換される。同時に、基準発振器12の出力信号は逓 倍回路14にも送られ、その周波数が逓倍されて連続周 期測定回路17、18のための計数クロックが作られ、 これら連続周期測定回路17、18に供給される。周波 数変換回路13からの試験信号はワンダ測定時の基準位 相となるもので、上述したように切り替え回路16及び 第2の分周器22を介して測定信号生成回路11へ入力 2として供給される。また、周波数変換回路13からの 試験信号は各種の試験、測定等に用いるために外部へジ ッタのない純粋の試験信号として出力されるとともに、 ジッタ付加回路15にも供給され、ジッタが付加された 試験信号が各種の試験、測定に用いるために外部へ出力 される。

【0024】ジッタ付加回路15は、例えば各種の装置や伝送路等で発生するジッタ、或いは1TU/TSで許容されている範囲内のジッタを人工的に発生させるもので、ユーザが設定できる任意の波形や周波数のジッタを周波数変換回路13からの基準位相の試験信号に付加回路15は周波数変換回路13からの基準位相の試験信号をデータ入力及び外部クロック入力としてジッタ付加試験信号を生成する。このジッタ付加回路15からのジッタ付加試験信号を失成する。このジッタ付加回路15からのジッタ付加試験信号を、例えばジッタ除去回路等の被試験装置、或いは交換機や伝送装置内のネットワーククロック供給装置等の被試験装置に入力し、それらの出力信

号を被測定信号として本解析装置に入力することによって、被試験装置のジッタ抑圧効果やジッタ耐力の解析、 不要ジッタ出力のチェック等を行うことができる。

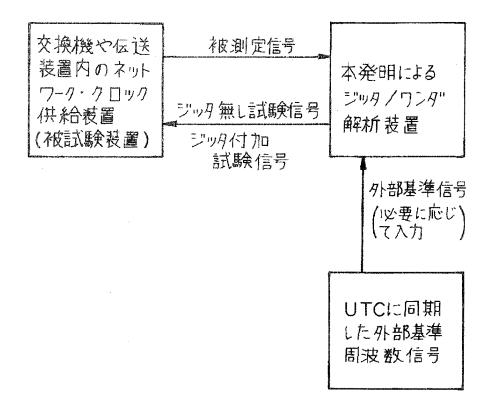

【0025】図2は本解析装置から試験信号(ジッタ無 し及びジッタ付加)を交換機や伝送装置内のネットワー ク・クロック供給装置 (被試験装置) に供給し、この被 試験装置からの出力信号を被測定信号として本解析装置 に入力することによって、被試験装置のジッタ抑圧効果 やジッタ耐力の解析、不要ジッタ出力のチェック等を行 う場合の回路構成の一例を示す。ネットワーク・クロッ ク供給装置の出力クロック信号の周波数は、一般的に、 1544KHz (北米、日本、一部の東南アジアの国) 又は2048KHz(これらの国以外の国々)のいずれ かであるので、これを被測定入力1として第1の分周器 21を介して測定信号生成回路11に入力する。分周周 波数を4KHzと決定したのは、ITU/TSの勧告書 に例として4KHェによるワンダ測定系統図が掲載され ているためであり、他の分周周波数を用いてもよいこと は勿論である。なお、比較的高い周波数のジッタを解析 する場合には、出力クロック信号を分周せずにそのまま 測定信号生成回路11に入力する。

【0026】上記構成において、切り替え回路16が被 測定入力2側に接続され、被測定入力1及び2としてパ ルス信号がそれぞれ第1及び第2の分周器21及び22 を介して測定信号生成回路11に供給されると、第1及 び第2の連続周期測定回路17及び18には、測定信号 生成回路11によって決定された被測定入力1及び2の パルス信号の立ち上がりエッジ(正のエッジ)又は立ち 下がりエッジ(負のエッジ)のいずれか一方のエッジ信 号が連続的に供給され、この供給された被測定エッジ信 号のエッジの発生周期が連続して測定される。測定結果 (周期データ) はデータライン170及び180を通じ て、また、書き込みパルスは書き込みライン17W及び 18Wを通じて、第1及び第2のバッファメモリ19及 び20にそれぞれ送られる。これらバッファメモリ1 9、20はデータライン17D及び18Dを通じて送ら れてくる測定データを書き込みライン17W及び18W を通じて供給される書き込みパルスによって漏れなく記 憶する。記憶されるデータ数はユーザが操作部60を通 じて予め設定する。ここでの測定結果を用いて次段の演 算解析部30が時間/周波数の諸量を算出する。

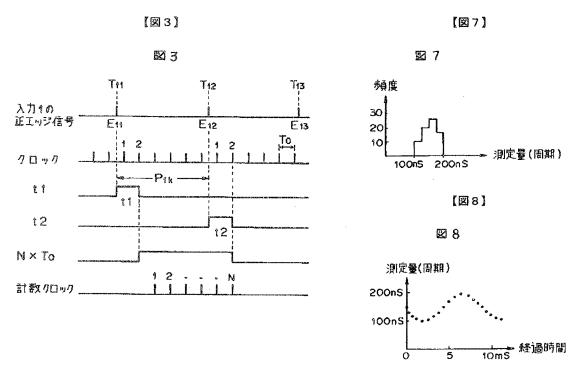

【0027】第1、第2の連続周期測定回路17、18は同じ構成のものでよく、周期の測定は、代表例として第1の連続周期測定回路17に被測定入力1の正のエッジが供給される場合について説明すると、図3に示すようにして行われる。例えば入力1の時刻T11における正のエッジE11と次の時刻T12における正のエッジE12間の時間である1つの被測定周期P1kは、図3に示すように、周期P1kの始端であるエッジE11から2つ目の計数クロック迄の時間t1と、周期P1kの後端であるエッジ

E12から2つ目の計数クロック迄の時間 t 2 と、時間 t 1 の終りから時間 t 2 の終りまでに含まれる計数クロックの数Nにこのクロックの周期 t 0 を求めれば、t 1 の関係が成立することより、

P1k = NT0 + t1 - t2

として算出することができる。

【0028】ここで、エッジから2つ目の計数クロックを選択したのは、1つ目の計数クロックを選択した場合にはエッジと1つ目の計数クロックとが極めて接近し、高精度のt1、t2の時間測定が行えないことがあり得るためであり、時間t1、t2の高精度の測定が行えれば、エッジの直後の1つ目の計数クロックを選択してもよいことは言うまでもない。

【0029】第1、第2の連続周期測定回路17、18は、上述のようにして算出したデータのうち、時間t1の終りから時間t2の終りまでに含まれる計数クロックの数Np1k、Np2kにこの計数クロックの周期T0を掛け算したデータ(時間に相当する)Np1k T0、Np2k T0はディジタル値であるのでそのまま出力し、一方、端数時間t1、t2についてはその差(t1-t2)

(端数量と称す)を電圧に変換し、さらにアナログーディジタル変換器(A/D変換器)でこれをディジタル値にしたΔVp1K、ΔVp2Kをデータライン17D、18Dを通じて第1、第2のバッファメモリ19、20に出力する。なお、計数値Np1k、Np2kのkはk=1~mであり、mはユーザが設定する測定回数である。また、この連続周期の測定結果の積算値がデータ取得時の時刻となる。従って、データ取得時の時刻も漏れなく測定されることになる。

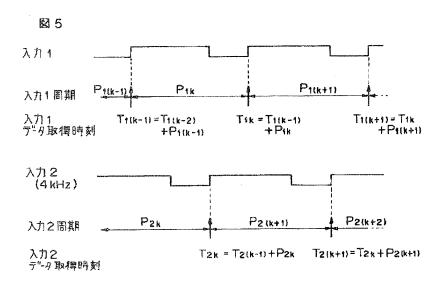

【0030】また、相対ジッタやワンダを測定する場合 には、2つの連続周期測定回路17及び18の周期デー タ取得時刻の差から時間間隔値を算出する必要があるた め、両者の測定開始時刻を合わせる必要がある。測定信 号生成回路 1 1 が例えば 4 K H z の被測定信号の正の工 ッジを入力1として第1の連続周期測定回路17に供給 し、入力2としてジッタ無しの4KHzの試験信号の正 のエッジを第2の連続周期測定回路18に入力する場 合、図4に示すように、測定が開始された後、第2の連 続周期測定回路18は、測定開始直後だけ、被測定信号 の立ち上がりから試験信号の立ち上がりを測定するよう に、測定信号生成回路11でシーケンスが組まれてい る。即ち、入力1の被測定信号の立ち上がりから測定が 開始され、第2の連続周期測定回路18はこの測定開始 時刻から時刻 T 21における試験信号の最初の立ち上がり までの時間 P21を測定し、初期時刻オフセット値(P2 1) として記憶して測定開始時刻を合わせる。

【0031】上述したように、第1及び第2のバッファメモリ19及び20は第1及び第2の連続周期測定回路 17及び18で測定された周期データを漏れなく記憶す る。これらバッファメモリ19、20に記憶されるデータ数はユーザが操作部60を通じて予め設定する。バッファメモリ19、20に記憶されたデータは、被測定信号における時間/周波数領域の諸量、例えば周期、時間間隔などを測定するために、また、これらの諸量の統計演算、度数分布、経過時刻に対する変化、MTIE演算、ジッタ周波数成分を解析するために、次段の演算解析部30で使用される。

【0032】演算解析部30は、本実施例では、第1及び第2の端数量加算部31及び32と、測定量演算部33と、解析演算部34とから構成されている。第1、第2の端数量加算部31、32は計数クロックで測りきれない端数量時間分電圧のディジタル値(ΔVplk、ΔVplk)を時間領域のデータに換算し、上述した計算式に基づいて、この換算データに、計数クロックによる周期データ(Nplk T0、Np2k T0)を加算して、最終的な周期データ(P1k、P2k)を算出する。即ち、

P1k=Np1k T0 + \( \D\) Vp1k

$P2k = Np2k T0 + \Delta Vp2k$

一例として、端数量時間 t 1 ー t 2 を Δ T n s 、 Np1k 及び Np2k を N 、 Δ Vp1k 及び Δ Vp2k を Δ V と置き、連続周期測定回路 1 7 及び 1 8 の A / D 変換器での端数 置時間分電圧のディジタルビット数を 1 2 ビットとし、計数クロックの周期 T 0 = 1 0 n s とした場合、 Δ T = -2 0 、 -1 0 、0、+1 0、+2 0 n s のとき、後述する連続周期測定回路 1 7 及び 1 8 のサンプルホールド回路の電圧が -2 0 4 8 、 -1 0 2 4 、 -2 0 4 8 m V 、また、 A / D 変換器の出力(Δ V)が 0、1 0 2 4、2 0 4 8、3 0 7 2、4 0 9 6 カウントであったとすると、求める周期 P(= P1k = P2 k)は

$P = NTO + \Delta T$

$=NT0 + (\Delta V - 2048) T0 / 1024$

$= T0 (N+\Delta V-2048) / 1024$

仮にTO=1000とすると、

$P = 1000 (N - 2 + \Delta V / 1024)$

となり、A/D変換器が1ビットの精度を持てばほぼ1 Opsまでの測定が可能となる。なお、10ns=10 24mVとするには、各端数時間測定回路の積分器の C、R、又は電圧を適度に設定すればよい。

【0033】測定量演算部33は端数量加算部31、32で得られた最終的な周期データを用いて被測定信号の周期Pnk、時間間隔Tkや測定データの取得時刻の算出演算を行う。ここで、nは入力チャネル番号(被測定入力1が供給されるチャネルが入力チャネル1、被測定入力2又は試験信号が供給されるチャネルが入力チャネル2)、k=1~mで、mはユーザが設定する測定回数を示す。以下に、被測定信号の周期Pnk及び時間間隔Tkを算出する方法について説明する。

【〇〇34】測定信号生成回路11の入力チャネル1、

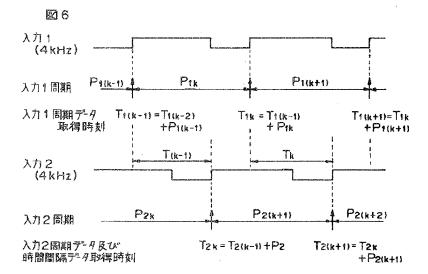

入力チャネル2に2系統の被測定信号(被測定入力1、被測定入力2又はジッタ無し試験信号)が供給されたときの周期Pnkは、第1、第2の端数量加算部31、32によって、上記計算式に基づいて入力チャネル1の被測定信号(入力1)の周期はP1k、入力チャネル2の被測定信号(入力2)の周期はP2kとして算出される。これら周期を図5に示す。この図5から明瞭なように、被測定信号の周期は両入力チャネルに供給される2系統の被測定信号について同時測定が可能である。

【0035】次に、入力チャネル1に供給される被測定信号と入力チャネル2に供給される被測定信号間の時間間隔を測定する場合について説明する。本明細書では同一レートの2つの信号の特定のエッジ間の差を「時間間隔」と称す。この時間間隔Tkは、図6から明瞭なように、入力2の正のエッジT2(k+1)(代表例)の時刻から入力1の正のエッジT1k(代表例)の時刻を減算することによって算出することができる。即ち、

Tk = T2(k+1) - T1k

ここで、T2(k+1)=T2k+P2(k+1)、T1k=T1(k-1)+P1kであるから入力1及び入力2の周期P1k及びP2(k+1)と正のエッジ発生時刻T1(k-1)及びT2kより時間間隔Tk を算出することができる。

【0036】上述のようにして測定量演算部33で演算された時間/周波数の諸量、本実施例では周期及び時間間隔は必要に応じて解析演算部34において解析される。主な解析方法は図1のブロック内に示したように、統計演算、度数分布、時刻変化(経過時間に対する変化)、MTIE演算、ジッタ周波数成分解析である。これら解析法について以下に簡単に説明する。

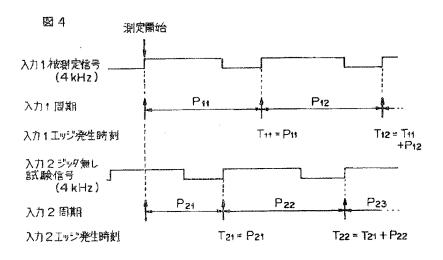

【0037】統計演算解析法は、算出したデータの平均、分散、標本分散、標準偏差、標本標準偏差、最大値、最小値、アラン分散、√アラン分散、正規化、±オフセット、定数乗除算により解析を行うものである。度数分布解析法は、図7に示すように、測定量例えば周期Pk (時間間隔でもよい)を横軸にとり、縦軸にその周期Pk が得られた数(頻度)をとり、度数分布を表示して解析を行うものである。

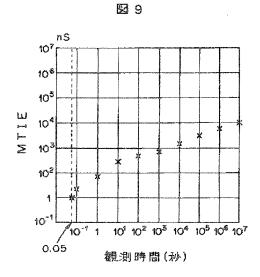

【〇〇38】時刻変化解析法は、図8に示すように、横軸に経過時間 t k をとり、縦軸に測定量例えば周期 P k をとって、周期 P k の時間に対する変化状態を表示し、解析を行うものである。次に、MTIE(MAXIMUM TIME INTERVAL ERROR、最大時間間隔エラー) 演算について説明する。

【0039】ワンダ測定において、ユーザが設定する観測時間内での時間間隔値の最大値から最小値を差し引き、それをMTIEとする。ユーザが設定する観測時間範囲は、ITU/TSの勧告と測定時間の現実性から考慮して、本実施例の解析装置では50m秒~107秒までの範囲とする。MTIE算出例を簡単に説明するために、以下の説明では観測時間の設定を、50m秒を除い

て、ディケード単位で段階的に設定するようにしているが、最小ステップ 2 5 0  $\mu$  s で、それ以外のさらに詳細な観測時間の設定も可能である。

【OO40】また、設定された観測時間以下の観測時間のMTIEも以下の要領で併せて算出可能であり、1回の測定で異なった観測時間のMTIEを算出してグラフ化できる。

観測時間のユーザ設定値の例:  $5 \times 10^{-2}$ s、10  $^{-1}$ s、100 s、10 $^{+1}$ s、10 $^{+2}$ s、10 $^{+3}$ s、10  $^{+4}$ s、10 $^{+5}$ s、10 $^{+6}$ s、10 $^{+7}$ s

以下に観測時間を最大の $10^{+7}$ sに設定した場合の例を記載する。

- a)測定開始後、最も短い観測時間である $5 \times 10^{-2}$ s 経過した時点での、時間間隔値の最大値 $\times$ max(1)と最小値 $\times$ min(1)を検出し、メモリに記憶する。測定は測定は そのまま続行する。

- b) さらに  $5 \times 10^{-2}$  s 経過の後、つまり測定開始から  $10^{-1}$  s 経過した時点での時間間隔の最大値  $\times$  max (2) と 最小値  $\times$  min (2) を検出し、メモリに記憶する。測定は測定はそのまま続行する。

- c) さらに  $9 \times 10^{-1}$  s 経過の後、つまり測定開始から  $10^0$  s 経過した時点での時間間隔の最大値  $\times$  max (3) と 最小値  $\times$  min (3) を検出し、メモリに記憶する。測定は測定はそのまま続行する。

- d)以下同じ要領で、設定観測時間の最大値 1 0+7 sが 経過するまで、各観測時間における時間間隔値の最大値 Xmax(n)と最小値 Xmin(n)を検出し、メモリに記憶す る。

- e) その後に、各観測時間の最大値 X max (n) から最小値 X min (n) を差し引き、M T I E を算出し、図 9 に示すような観測時間対M T I E のグラフを表示する。

[0041]MTIE=Xmax(n)-Xmin(n)

f) また、このようにして算出したMTIEから、長期 周波数偏差( $\Delta$ f/f)を算出する。

## Δf/f=MTIE/観測時間

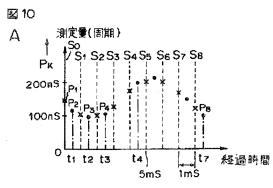

ジッタ周波数成分解析法は、測定された周期や時間間隔の経過時間に対する変化量をFFT部(高速フーリエ変換部)で高速フーリエ変換し、ジッタの周波数スペクトラムを導いて解析を行うものである。ただし、本装置で得られた測定量データは一定の時間間隔で測定されたものではないため、補間部において測定量データとその取得時刻データから補間法を用いて一定間隔で測定された場合の測定量データに変換する。

《0042》この補間部における補間法の一例を示すと、演算解析部 300第1、第20端数量加算部 31、32で得られた各測定周期データをP1, P2, P3。。 とすると、これら周期データは各測定サイクルごとにそれまでの測定値が加算され、P1 = t1, P1 + P2 = t2, P1 + P2 + P3 = t3, . . . . として経過時間メモリ(図示せず)に記憶される。これら t1, t

$2 \cdot t_3 \cdot t_3 \cdot t_3$  、・・・は測定開始からの時刻を示しており、時刻 0 のときに周期の測定値  $P_1$  が得られ、時刻  $t_1$  のときに周期の測定値  $P_2$  が得られ、時刻  $t_2$  のときに周期の測定値  $P_3$  が得られていることになる。これらから周期  $P_k$  の変化の時間経過を示すと、例えば図 1 0 A に示すように、測定値  $P_k$  は不等時間間隔で得られている。

【0043】これら測定周期データPk から、等時間間 隔で得られたと見なせる周期データPskを補間部で算出 する。例えば図10Aにおいて、時刻0から等時間間隔 の標本点S0 、 S1 、 S2 、 ・・・で周期を測定したと みなせる周期データを、最も利用し易い直線補間法を使 って求める。8つの測定周期データPk は(tk. Pk ) 座標で1 (0, P<sub>1</sub>), 2 (t<sub>1</sub>, P<sub>2</sub>), 3 (t<sub>2</sub> , P<sub>3</sub>), 4 (t<sub>3</sub>, P<sub>4</sub>), · · · 8 (t<sub>7</sub>, P g) と表わせる。標本点SOの周期は当然P1でよい。 標本点S1は次のようにして求める。即ち、図10Bに 示す3点(t1, P2), (S1, Ps1), (t2, P 3) を通る直線44がP=At +Bであるとすると、  $A = (P_2 - P_3) / (t_1 - t_2)$  $B = (t_1 P_3 - t_2 P_2) / (t_1 - t_2)$ となる。このA、BとSIとを直線の式に代入すると、  $Ps_1=S_1 (P_2-P_3) / (t_1-t_2) + (t_1 P_1)$ 3 - t2 P2) / (t1 - t2)で標本点S1 の周期Ps1が求まる。以下、同様にして周

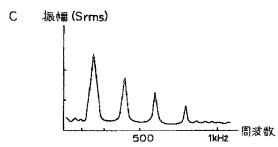

期Ps2、Ps3、Ps4、・・を求める。 【0044】このようにして得られた等時間間隔の周期データPsk(図10Aの×印のデータ)をFFT部で高速フーリエ変換する。この変換結果の周波数スペクトラムを表示部50の表示器(図示せず)に表示することにより、例えば図10Cに示す表示が得られる。これよが問期Pkの変動(ジッタ)の周波数成分を知ることもり、周期Pkの値、又はその平均値を対する。このとき、周期Pkの値、又はその平均値を対するとして表示したり、上記周波数スペクトラムをPkに対する比として表示することもできる。さらに、そのジッタの周期に対する百分率を求めることもできる。等時間間で得られたと見なせる周期データPskの精度を上げるために、スプライン法その他の補間法を用いることもできる。

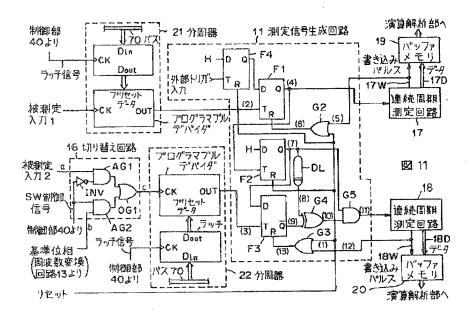

【0045】次に、本装置の各部をさらに詳細に説明する。測定部10は可能な限り取り落とすことなく連続的にデータを取得し、かつデータ取得時の時刻(経過時間)を正確に知ることができることが望まれる。まず、図11を参照して測定信号生成回路11、切り替え回路16、並びに第1及び第2の分周器21及び22の一具体例について説明する。

【0046】測定信号生成回路11は、第1、第2、第 3及び第4の4つのD形フリップフロップF1、F2、 F3及びF4と、2つのORゲートG2、G3と、1つ の排他的ORゲートG4と、1つのANDゲートG5 と、1つの遅延回路DLとから構成されており、第1の 分周器21からの入力1は第1のD形フリップフロップ F1のトリガ端子Tに供給され、また、第2の分周器2 2からの入力2は第3のD形フリップフロップF3のト リガ端子Tに供給される。

【OO47】一方、測定を開始させるための外部トリガ入力信号は第4のD形フリップフロップF4のトリガ端子Tに供給され、そのデータ端子Dに与えられている高レベル信号Hがその出力端子Qから第1のD形フリップフロップF1の出力端子Qは第1の連続周期測定回路17及び第2のD形フリップフロップF2のトリガ端子Tにそれぞれ接続されており、そのデータ端子Dに与えられている高レベル信号Hがその出力端子Qから出力される。

【〇〇48】第2のD形フリップフロップF2のデータ端子口にも高レベル信号Hが与えられており、その出力端子Qは第3のD形フリップフロップF3のデータ端子 D及びANDゲートG5の一方の入力に接続されるとともに、遅延回路DLを介して排他的ORゲートG4の一方の入力には第3のD形フリップフロップF3の出力端子 Q(Qの論理反転)が接続され、この排他的ORゲートG4の出力はANDゲートG5の出力は第2の連続周期測定回路18に接続されている。これら遅延回路DL、排他的ORゲートG4及びANDゲートG5はパルス波形を整形するパルス整形機能部として働く。

【0049】第1及び第2の分周器21及び22は同じ構成のものであり、第1の分周器21は1つのプログラマブルデバイダPD1と1つのラッチLT1とから、また、第2の分周器22も1つのプログラマブルデバイダPD2と1つのラッチLT2とからそれぞれ構成され、上述したように測定条件に応じて分周比が切り替えられるようになっている。これら、プログラマブルデバイダPD1、PD2のプリセットデータ端子にはラッチLT1、LT2からユーザによって予め設定されたデータがそれぞれ入力される。

【0050】切り替え回路16は2つのANDゲートAG1、AG2と、1つのインバータINVと、1つのORゲートOG1とから構成された論理的スイッチであるが、リレー等の機械的スイッチを用いることもできる。この切り替え回路16は、制御部40からスイッチ(SW)制御信号(高レベル)が入力されると、周波数変換回路13からの基準位相の試験信号を第2の分周器22に供給し、また、制御部40からスイッチ(SW)制御信号が入力されないときには(或いは低レベルのスイッチ制御信号が入力されると)、被測定入力2を第2の分周器22に供給する。

【〇〇51】上記構成によれば、測定信号生成回路11

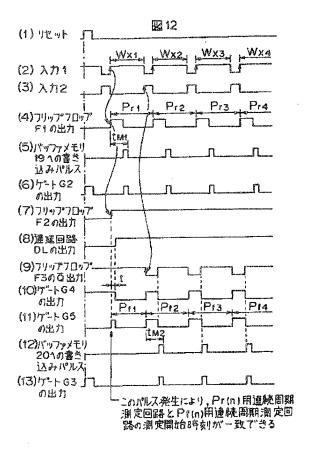

の第4のD形フリップフロップF4のトリガ端子Tに外 部トリガ信号が入力されることにより測定動作が開始さ れ、また、制御部40から入力されるスイッチ制御信号 で切り替え回路16が被測定入力2を供給するか基準位 相の試験信号を供給するかを決定し、測定信号生成回路 11に入力1、入力2が供給されてその被測定エッジが 連続的に発生され、第1、第2の連続周期測定回路1 7、18へ供給されることは明白であるので、図11中 に(1)~(13)で指示した各部の波形を図12に示 し、その動作説明を省略するが、図12の波形は、入力 1として図示するようなパルス幅Wx1、Wx2、Wx3、・ ・・の正のパルス信号が第1のD形フリップフロップF 1のトリガ端子Tに入力され、入力2として入力1の波 形を反転した形式の正のパルス信号が第3のD形フリッ プフロップF3のトリガ端子Tに入力された場合のもの である。

【0052】若干の説明を付加すると、リセットパルス (波形(1)参照)により、第2、第4のD形フリップ フロップF2、F4は直接リセットされ、第1のD形フ リップフロップF1はORゲートG2を介して、第3の D形フリップフロップF3はORゲートG3を介してそ れぞれリセットされ、同時にこのリセットパルスにより 第1、第2の連続周期測定回路17、18もリセットさ れる。また、入力1の立ち上がりエッジにより第1のD 形フリップフロップF1の出力Qが反転し、これにより 第1のD形フリップフロップF1が作動するが、第1の D形フリップフロップF1の出力Qが反転した後、一定 時間経過後に第1の連続周期測定回路17が書き込みパ ルス (波形 (5) 参照) を発生してパッファメモリ19 へ測定データ (立ち上がりエッジ間の周期Pr1, Pr2, ・・・)を書き込むようになっている。これは第1の連 続周期測定回路17が内部処理に要する時間を見込んだ ためである。図12における時間tMがこの内部処理に 要する時間を見込んだ時間(書き込みパルス(5)の発 生を含む)である。

【0053】第2の連続周期測定回路18の場合も同様であり、入力1のパルス幅Wx1の後端の立ち下がりエッジと同時刻の入力2(波形(3)参照)の立ち上がりエッジにより第3のD形フリップフロップF3の出力Qが反転し、これより一定時間経過後に第2の連続周期測定回路17が書き込みパルス(波形(12)参照)を発生してバッファメモリ20へ測定データ(立ち下がりエッジ間の周期Pf1、Pf2、・・・)を書き込むようになっている。図12における時間tM2がこの内部処理に要する時間を見込んだ時間(書き込みパルス(12)の発生を含む)である。

【0054】これら書き込みパルス(5)及び(12)の発生により第1及び第3のD形フリップフロップF1及びF3はORゲートG2及びG3を通じてリセットされるが、第2のD形フリップフロップF2はリセットパ

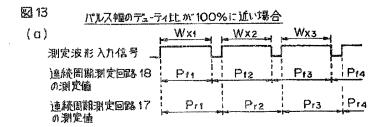

ルスが供給されないのでその出力Qは高レベルのままで ある。ここで、第2のD形フリップフロップF2の出力 Qは遅延回路DLで時間tだけ遅延されて排他的ORゲ ートG4の一方の入力に供給されるため、ANDゲート G5から最初に継続時間tのパルス(液形(11)参 照)が発生される。このパルスの発生により第1、第2 の連続周期測定回路17、18の測定開始時刻が一致で きる。また、ANDゲートG5から出力される立ち下が リエッジ間の周期Pf1、Pf2、・・・のうち、最初の周 期Pf1は入力1のパルス幅Wx1に等しい。このようにし て各バッファメモリ19、20に書き込まれたデータ内 容(デューティ比が100%に近い場合)を図13に示 す。図13において(a)は測定値と入力1のパルス信 号との関係を示し、(b)はバッファメモリ19、20 の内容を示す。この場合のパルス幅の演算式は次の通り である。

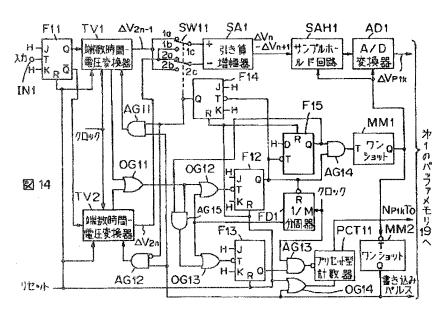

【0055】パルス幅Wxn=Wx(n-1)+Pfn+Pr(n-1) 次に、第1、第2の連続周期測定回路17、18の一具 体例について図14を参照して説明する。これら連続周 期測定回路17、18としては、例えば特願昭62-2 5326号に示す技術を基本構成として利用することが できる。上述したように、第1、第2の連続周期測定回 路17、18の回路構成は実質的に同じものでよく、図 3を参照して説明したように、端数時間 t1、t2と、 時間 t 1の終りから時間 t 2 の終りまでに含まれる計数 クロックの数Np1k、Np2k にこの計数クロックの周期 TO を掛け算したデータNp1K TO 、Np2K TO とを算 出し、この算出したデータのうち、Np1K TO、Np2K T0 はそのまま出力し、端数時間 t1 、 t2 については その差(t1 -t2 )を電圧に変換し、さらにA/D変 換器でこれをディジタル値にしたΔVp1K、ΔVp2Kを 出力できる回路構成であればよく、図14は特願昭62 -25326号に示す技術を基本構成とし、上記動作が 行えるようにこれを一部変更した第1の連続周期測定回 路17の一具体例を示す。勿論、第2の連続周期測定回 路18も同様の回路構成のものでよく、また、図14の 回路構成に限定されるものではない。

【0056】図14に示す連続周期測定回路17は、第1~第4の4つのJKフリップフロップF11~F14と、1つのD形フリップフロップF15と、第1及び第2の端数時間一電圧変換器TV1及びTV2と、第1~第5の5つのANDゲートAG11~AG15と、第1~第4の4つのORゲートOG11~OG14と、第1及び第2の端数時間一電圧変換器TV1及びTV2の出力値間の減算を行う引き算増幅器SA1と、第1及び第2の端数時間一電圧変換器TV1及びTV2の出力値を引き算増幅器SA1に切り替えて入力することが可能な切り替えスイッチSW11と、クロックを1/Mに分間する1/M分周器FD1と、第1及び第2の2つのワンショットマルチバイブレータMM1及びMM2と、Np1

K T0 を計数するプリセット型計数器PCT11と、端数量(t1-t2)電圧をサンプルホールドするサンプルホールドするサンプルホールドするサンプルホールド回路SAH1と、サンプルされた端数量電圧をディジタル信号に変換するアナログーディジタル変換器(A/D変換器)AD1とから構成されている。これら構成要素の接続状態は図示の通りであるのでその説明を省略する。なお、第1~第4の各JKフリップフロップF11~F14のJ及びK端子と、D形フリップフロップF15のデータ端子Dとにそれぞれ供給されているHは高レベル信号を表す。

【0057】上記構成において、入力端子IN1には測定信号生成回路11から入力1の被測定エッジ信号が供給される。(第2の連続周期測定回路18の場合には入力端子IN1に測定信号生成回路11から入力2の被測定エッジ信号が供給されることになる。)以下の動作説明は第1の連続周期測定回路17の場合であるが、第2の連続周期測定回路18の場合も同様の動作を行うことは置うまでもない。

【0058】入力端子IN1に供給された入力1の被測 定エッジ信号は第1のJKフリップフロップF11のト リガ (クロック) 入力端子Tに入力され、第1番目のエ ッジ信号によってレベル反転したJKフリップフロップ F11の出力Qが第1の端数時間一電圧変換器TV1に 供給される。第1の端数時間一電圧変換器TV1はこの エッジ (例えば図3のE11) から2つ目の計数クロック 迄の時間 t1 (図3参照)を算出してこれを電圧信号△ V1に変換する。また、JKフリップフロップF11の 出力 Q(Qの論理反転出力)は第2の端数時間一電圧 変換器TV2に接続されており、次に入力する被測定工 ッジ信号(2番目のエッジ信号)によってレベル反転し た出力。Qがこの第2の端数時間一電圧変換器TV2に 供給されると、第2の端数時間一電圧変換器TV2はこ のエッジ (例えば図3のE12) から2つ目の計数クロッ ク迄の時間 t 2 (図3参照)を算出してこれを電圧信号 △∨2に変換する。以下同様にして第1の端数時間一電 圧変換器TV1は第3、第5、・・・の奇数番目のエッ ジから2つ目の計数クロック迄の時間に対応する電圧信 号 △ ∨ 2n-1を発生し、第 2 の端数時間 一電圧変換器 T ∨ 2は第4、第6、・・・の偶数番目のエッジから2つ目 の計数クロック迄の時間に対応する電圧信号 A V2nを発 生することになる。

【0059】これら電圧信号ΔV2n-1及びΔV2nは切り替えスイッチSW11を介して引き算増幅器SA1に供給される。この切り替えスイッチSW11は連勤動作する2つの切り替えスイッチよりなり、第1の切り替えスイッチの可動接点1cは引き算増幅器SA1の+側入力に接続され、その一方の固定接点1aは第1の端数時間一電圧変換器TV1の出力側に、他方の固定接点1bは第2の端数時間一電圧変換器TV2の出力側にそれぞれ接続され、また、第2の切り替えスイッチの可動接点2

cは引き算増幅器SA1の一側入力に接続され、その一方の固定接点2aは第2の端数時間一電圧変換器TV2の出力側に、他方の固定接点2bは第1の端数時間一電圧変換器TV1の出力側にそれぞれ接続されている。

《OO60》引き算増幅器SA1における演算は、上述 したように端数量(t1-t2)の電圧を求めるもので あるから、始端側の電圧から終端側の電圧を減算する。 従って、初期設定時に切り替えスイッチSW11の可動 接点は図示する位置にあり、始めに (ΔV1-ΔV2) の引き算が行われる。なお、引き算増幅器SA1におけ る演算は常に始端側の電圧から終端側の電圧を減算する 演算であるが、次の引き算においては直前の終端側の電 圧 (Δ V 2) が始端側の電圧として利用できるので、ス イッチSW11を切り替えて第2の端数時間一電圧変換 器TV2の出力(△∨2)から第1の端数時間−電圧変 換器TV1の2番目の出力(ΔV3)を引き算すること になる(△∨2-△∨3)。その次の引き算は再びスイ ッチSW11を切り替えて第1の端数時間一電圧変換器 TV1の2番目の出力 (△∨3) から第2の端数時間-電圧変換器 T V 2 の 2 番目の出力 (Δ V 4) を引き算し (Δ∨3-Δ∨4)、以下交互にスイッチSW11を切 り替えて引き算を行うことになる。

【0061】このようにして算出した端数量電圧( $\Delta V$   $n-\Delta V$ n+1)をサンプルホールド回路SAH1でサンプルし、さらにA/D変換器AD1でこれをディジタル値に変換した端数量電圧のディジタル値 $\Delta V$ piKを第1のバッファメモリ19へ出力する。また、時間 tnの終りから時間 t (n+1)の終りまでに含まれる計数クロックの数Npik にこの計数クロックの周期T0を掛け算したデータNpiK T0 はプリセット型計数器PCT11より第1のバッファメモリ19へ出力される。

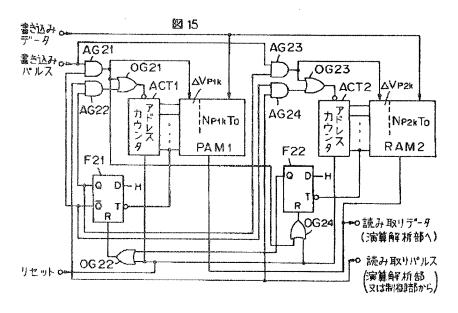

『0062》一方、第2のワンショットマルチバイブレ ータMM2から発生される書き込みパルスは第1のバッ ファメモリ19に供給され、入力される測定データの書 き込みを開始させる。よって、これら周期データより演 算解析部30において上述したようにして被測定信号の 周期を連続して測定することができる。次に、第1、第 2のバッファメモリ19、20の一具体例を図15に示 す。書き込みパルスが入力されたときに測定部10から のデータを連続的に漏れなく記憶するため、各バッファ メモリ19、20はそれぞれ二重バッファとされ、同規 槙の2組のアドレスカウンタ(ACT1、ACT2)と RAM (RAM1、RAM2) が使用され、それらは交 互に書き込み動作をする。また、一方のアドレスカウン タとRAMに書き込み動作を行っている間は、他方のア ドレスカウンタとRAMは読み出される。必要に応じて 審き込みよりも読み取りの速度を上げて、読み取り後、 次にそのバッファメモリに対する書き込みが行われるま での時間に必要な演算を行うことができるようにしても よい。図15には第1のバッファメモリ19の一具体例 を示すが、第2のバッファメモリ20も同様の回路構成で良く、第1、第2の連続周期測定回路17、18からの書き込みデータ(周期データ)Np1K T0、Np2K T0及び $\Delta$ Vp1K、 $\Delta$ Vp2K はこれら連続周期測定回路17、18から書き込みパルスが供給されると、各バッファメモリ19、20のRAMに区別されて記憶される。なお、図15中、AG21~AG24はANDゲートを、OG21~OG24はORゲートを、F21及びF22はD形フリップフロップをそれぞれ示す。

【0063】上述したように、これらバッファメモリ19、20は、メモリアドレスがアドレスカウンタの最終値に来たら初期値へ戻る巡回型に構成され、演算解析部は測定値取得と平行してバッファメモリ19、10から測定値を読み出して、ユーザが設定する観測時間内における時間間隔値の最大値と最小値の算出を逐次行うようにする。

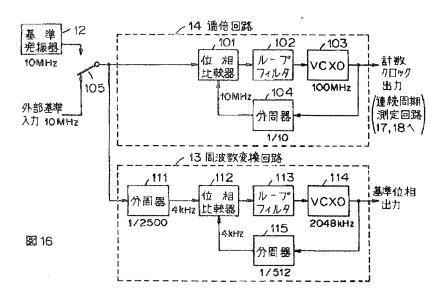

【0064】次に、周波数変換回路13及び逓倍回路1 4の一具体例を図16に示す。これらは一具体例として 次の一般的な条件の場合の回路図である。

基準発振器出力周波数: 10MHz 外部基準入力周波数 : 10MHz 計数クロック周波数 : 100MHz 基準位相出力周波数 : 2048KHz

逓倍回路14は基準発振器12の出力周波数をPLL (フェーズロックループ) によって計数クロック周波数 に変換するものである。計数クロック周波数は市販の汎 用ディジタルIC(TTL、C-MOS、ECL等)で 構成できるように100MHz程度とし、PLLを構成 する電圧制御発振器(VCO)は位相雑音が低いクリス タル発振器を用いたもの(VCXO)を使用している。 【0065】逓倍回路14を構成するPLLは、通常の ように、基準発振器12の出力周波数信号が入力される 位相比較器101と、この位相比較器101からの出力 信号をフィルタするループフィルタ102と、このルー プフィルタ102でフィルタされた信号の電圧によって 発振周波数が制御されるVCXO103と、このVCX 〇103からの発振出力の周波数を1/10に分周する 分周器104とからなり、この分周器104の分周出力 が位相比較器101に入力され、基準発振器12からの 出力信号の位相と比較される。分周器104で1/10 に分周するのは基準発振器12の出力周波数が10MH zで、VCXO103の発振周波数が100MHzに設

【0066】なお、本例では基準発振器12からの出力 信号は切り替えスイッチ105を介して逓倍回路14及 び周波数変換回路13へ入力される。スイッチ105は 基準発振器12からの出力信号と外部基準周波数信号

定されているからである。

(例えばUTCに同期したもの)とを切り替えるもので、基準発振器12の発振周波数と同じ周波数の外部基準信号が得られるときには基準発振器12の代わりにこ

の外部基準周波数信号を使用することができるようになっている。よって、この場合には基準発振器 1 2 を設けなくてもよい。

【0067】また、回路規模は若干大きくなるが、PL しを使わずにオーバードライブ回路とチューニング・フ ィルタにより逓倍回路14を構成してもよい。ただし、 チューニング・フィルタは温度変化に強く、しかもQが 高いものを選定する。周波数変換回路13は基準発振器 の出力周波数をPLLによってワンダ測定時に必要な基 準位相信号に変換するものである。基準位相であるた め、この周波数変換回路13を構成するPLLの電圧制 御発振器(VCO)も位相雑音が低いクリスタル発振器 を用いたVCXOを使用している。周波数変換回路 13 を構成するPLLは、基準発振器 1 2 からの出力周波数 又は外部基準周波数信号(10MHェ)を分周器111 で1/2500に分周し、4KHzの信号を位相比較器 112に入力する点と、VCXO114から2048K Hzの周波数信号を発振させ、これを分周器115で1 /512に分周した4KHzの信号を位相比較器112 に入力する点を除くと、上記逓倍回路14のPLLと同 じ構成及び動作であるので、その説明を省略する。な お、位相比較器112の出力信号はループフィルタ11 3でフィルタされてVCXO114に入力される。

【0068】この周波数変換回路13からの基準位相の周波数信号(試験信号)は、上述したように切り替え回路16及びジッタ付加回路15に供給される。また、図示しない端子からジッタ無し試験信号出力として外部に取り出される。本例では2048KHzの試験信号を元が、試験信号としては主に1544KHzにする場合には設定値を変更すればよい。ユーザはその国によって必要ないずれか一方の試験周波数信号があればよいので、両方の周波数信号を発生させることは必ずしも必要でない。従って、実際は、この周波数変換回路13をオプションボードに載置すれば、ボード交換で簡単にユーザが試験周波数を変更することができる。

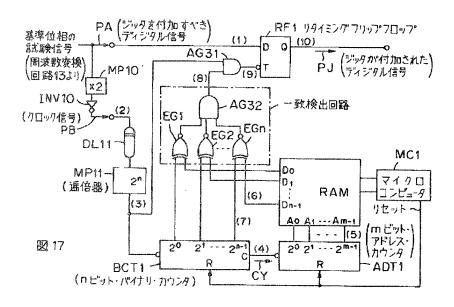

【0069】次に、ジッタ付加回路15の一具体例を図17に示す。このジッタ付加回路15は、例えば各種の装置や伝送路等で発生するジッタ、或いはITU/TSで許容されている範囲内のジッタを人工的に発生させるもので、ユーザが設定できる任意の波形や周波数の姿を周波数変換回路13からの基準位相の試験信号に付加すべき基準位相の試験信号PA(ディジタル信号)をリタイミングするリタイミングフリップフロックに多いをであためにこれを2倍する逓倍器MP10と、このインバータINV10の反転出力を遅延する遅延回路DL11と、遅延されたクロック信号を2n倍す

る2n 逓倍器MP11と、nビットのバイナリカウンタBCT1と、mビットのアドレスカウンタADT1と、RAMと、マイクロコンピュータMC1と、ANDゲートAG31及びAG32と、排他的ORゲートEG1、EG2、・・・EGnとから構成され、ANDゲートAG32と排他的ORゲートEG1、EG2、・・・EGnとにより一致検出回路を構成している。

【0070】ジッタ付加回路15は、周波数変換回路1 3からの基準位相の試験信号を、ジッタを付加すべきデ ィジタル信号PAとして、リタイミングフリップフロッ プRF1のデータ端子Dに入力し、一方、基準位相の試 験信号を逓倍器MP10に与えて2倍し、さらにインバ 一タINV10で反転して外部クロック信号PBを生成 し、このクロック信号PBから、マイクロコンピュータ MC1の制御の下で、2n 逓倍器MP11、nビットの バイナリカウンタBCT1、mビットのアドレスカウン タADT1、RAM、ANDゲートAG31及びAG3 2、排他的ORゲートEG1、EG2、・・・EGnに よって上記ディジタル信号PAをリタイミングするトリ ガ信号を作り、これをANDAG31からリタイミング フリップフロップRF1のトリガ端子Tに与え、リタイ ミングフリップフロップRF1の出力端子Qからジッタ が付加されたディジタル信号PJ(試験信号)を出力す るものである。

【 O O 7 1 】このジッタ付加回路 1 5 からのジッタ付加 試験信号 P J を、例えばジッタ除去回路等の被試験装 置、或いは交換機や伝送装置内のネットワーククロック 供給装置等の被試験装置に入力し、それらの出力信号を 被測定信号として本解析装置に入力することによって、 被試験装置のジッタ抑圧効果やジッタ耐力の解析、不要 ジッタ出力のチェック等を行うことができる。

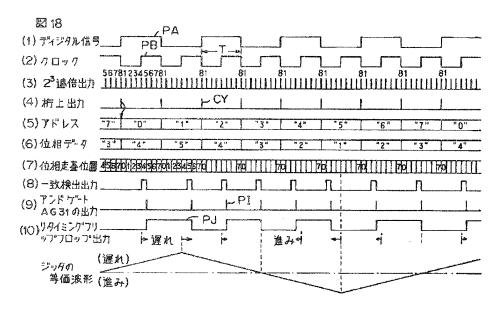

【0072】なお、上記ジッタ付加回路15の詳細な動作説明は本出願人が出願した特願平3-188723号「ジッタ付加装置」に記載されているので、ここでは図17における定数m及びnをそれぞれ3とした場合の各部の波形(1)~(10)を図18に示し、その説明を省略する。また、上記実施例はこの発明の単なる例示に過ぎず、従って、その構成や回路接続、使用する素子等は必要に応じて種々に変更及び変形できることは言うまでもない。

#### [0073]

【発明の効果】以上説明したように、この発明によれば、2系統の連続周期測定回路にパルス状の被測定信号の立ち上がりエッジ又は立ち下がりエッジを入力してその周期を連続的に測定することができ、また、解析手段が、算出された各々の測定値の経過時間に対する変化量を高速フーリエ変換して解析する手段を有するので、高速フーリエ変換した結果から2つの被測定信号のジッタ周波数スペクトラムを同時に、しかも高精度に求めることができるという効果がある。

【0074】また、測定量演算手段で各々の周期測定値より両信号間の時間間隔値を算出し、前記解析手段により、この時間間隔値の経過時間に対する変化量を高速フーリエ変換して解析することにより、相対的なジッタ周波数スペクトラムを高精度に求めることができるという効果がある。また、分周手段により被測定信号を適当な 周波数まで分周し、その分周周期を連続周期測定回路で 測定することによって全体の測定時間を長くすることができるから、前記解析手段により、算出された測定値の 経過時間に対する変化量を高速フーリエ変換して解析することにより、被測定信号の比較的低いジッタ周波数スペクトラムを高精度に求めることができるという効果がある。

【〇〇75】また、分周手段により被測定信号と基準位相の所定の周波数の試験信号とをそれらの周波数が一致する適当な周波数までそれぞれ分周し、各々の分周信号の周期を連続周期測定回路でそれぞれ測定し、測定量演算手段で各々の分周周期測定値より両信号間の時間間隔値を算出し、前記解析手段により、この両信号間の時間間隔値よりその最大値と最小値をそれぞれ算出するとともに、それらから複数の観測時間におけるMTIEや長期周波数偏差を同時に算出することにより、長期的位相変動であるワンダを効率よく解析することができるという効果がある。

【0076】また、基準位相の所定の周波数の試験信号にジッタを付加して、このジッタ付加試験信号を外部へ出力するジッタ付加手段を設けることにより、このジッタ付加手段からユーザが設定できる任意の波形や周波数のジッタ付加試験信号を外部の被試験装置に出力することができるから、該被試験装置からの出力信号を被測定信号として入力することにより、該被試験装置のジッタ抑圧効果やジッタ耐力を高精度に解析できるという効果がある。

【〇〇77】さらに、基準位相の所定の周波数の試験信号を外部へ出力するための端子を設け、この端子よりジッタのない純粋な試験信号を外部の被試験装置に出力して該被試験装置からの出力信号を被測定信号として入力することにより、該被試験装置のみで発生するジッタを高精度に解析できるという効果もある。従って、この発明によれば、低周波から高周波までの連続的なジッタ周波数成分解析を高精度に行うことができ、また、低周波ジッタの解析も十分に行え、さらに、ワンダに関してもエエリ/TSで勧告しているMTIEによるワンダを重要視されている50m秒から10~秒までの観測期間にわたって高精度に、効率よく測定することができる。

## 《図面の簡単な説明】

【図1】この発明によるジッタ/ワンダ解析装置の一実 施例の全体構成を示すブロック図である。

【図2】図1のジッタ/ワンダ解析装置により外部の被 試験装置のジッタ/ワンダを測定、解析する場合の一例 を示す構成図である。

【図3】図1のジッタ/ワンダ解析装置の連続周期測定 回路での連続周期測定動作を説明するための波形図であ る。

【図4】図1のジッタ/ワンダ解析装置において2つの 連続周期測定回路の測定開始時刻を合わせる方法を説明 するためのタイムチャートである。

【図5】図1のジッタ/ワンダ解析装置において入力パルスの周期を測定する場合の動作を説明するためのタイムチャートである。

【図6】図1のジッタ/ワンダ解析装置において2つの 入力パルス間の時間間隔を測定する場合の動作を説明す るためのタイムチャートである。

【図7】度数分布表示により算出したデータの解析を行 う一例を示す図である。

【図8】時間変化表示により算出したデータの解析を行う一例を示す図である。

【図9】MTIEを算出する動作を説明するための図である。

【図10】Aはパルス幅の時間経過を示す図、Bは直線 補間を説明するための図、Cはパルス幅ジッタの周波数 スペクトラムの例を示す図である。

【図11】図1のジッタ/ワンダ解析装置に使用された 測定信号生成回路、分周器及び切り替え回路の一具体例 を示す回路図である。

【図12】図11の測定信号生成回路の各部における信 号波形を示すタイムチャートである。

【図13】入力パルスのデューティ比が100%近い場合の連続周期測定回路での測定値とバッファメモリに記憶される内容との関係を示す図である。

【図14】図1のジッタ/ワンダ解析装置に使用された 連続周期測定回路の一具体例を示す回路図である。

【図15】図1のジッタ/ワンダ解析装置に使用された バッファメモリの一具体例を示す回路図である。

【図16】図1のジッタ/ワンダ解析装置に使用された 周波数変換回路及び逓倍回路の一具体例を示す回路図で ある。

【図17】図1のジッタ/ワンダ解析装置に使用された ジッタ付加回路の一具体例を示す回路図である。

【図18】図17のジッタ付加回路の各部における信号 波形を示すタイムチャートである。

#### 【符号の説明】

| 1 0    | 測定部      |

|--------|----------|

| 1 1    | 測定信号生成回路 |

| 1 2    | 基準発振器    |

| 1 3    | 周波数変換回路  |

| 1 4    | 逓倍回路     |

| 1 5    | ジッタ付加回路  |

| 1 6    | 切り替え回路   |

| 17, 18 | 連続周期測定回路 |

| 19,20 | バッファメモリ | 3 4 | 解析演算部 |

|-------|---------|-----|-------|

| 21,22 | 分周器     | 4 0 | 制御部   |

| 3 0   | 演算解祈部   | 5 0 | 表示部   |

| 31,32 | 端数量加算部  | 6 0 | 操作部   |

| 3 3   | 測定量演算部  | 7 0 | バス    |

[図1]

[図2]

## 図 2

【図4】

[図5]

【図6】

[図9]

【図10】

【図11】

[図12]

【図13】

## (b) 測定値

|        | メモリ20の内容 | メモリ19の内容 |

|--------|----------|----------|

| アドレス 0 | Pri      | ×        |

| 1      | Pt2      | Pri      |

| 2      | P13      | Pr2      |

| 3_     | P14      | Pr3      |

|        | 9        |          |

【図14】

[図15]

[図16]

[図17]

[図18]